### **Discontinued Product**

This device is no longer in production. The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: August 27, 2012

### **Recommended Substitutions:**

For existing customer transition, and for new customers or new applications, contact Allegro Sales.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

#### **Features and Benefits**

- Ultra small 2 × 2 DFN/MLP-8 package

- Low quiescent current draw (0.5 μA max. in shutdown mode)

- Primary-side output voltage sensing; no resistor divider required

- Fixed 1.5 A peak current limit

- 1.3 V logic (V<sub>HI</sub>(min)) compatibility

- Integrated IGBT driver with internal gate resistors

- Optimized for mobile phone, 1-cell Li+ battery applications

- Zero-voltage switching for lower loss

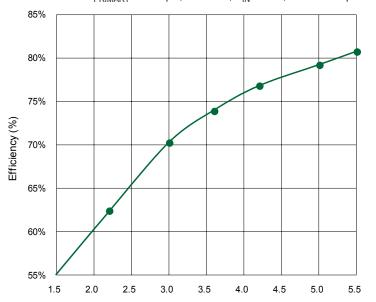

- >75% efficiency

- Charge complete indication

- Integrated 50 V DMOS switch with self-clamping protection

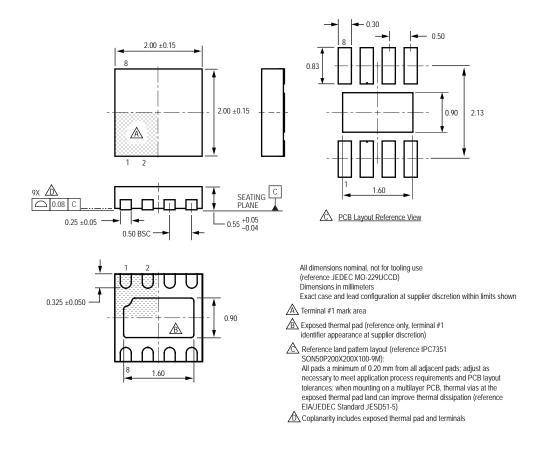

### Package: 8-pin DFN/MLP (suffix EE)

2 mm × 2 mm, 0.60 mm height

Not to scale

### **Description**

The Allegro® A8740 is a Xenon photoflash charger IC designed to meet the needs of ultra low power, small form factor cameras, particularly camera phones. By using primary-side voltage sensing, the need for a secondary-side resistive voltage divider is eliminated. This has the additional benefit of reducing leakage currents on the secondary side of the transformer. To extend battery life, the A8740 features very low supply current draw (0.5  $\mu A$  max in shutdown mode). The IGBT driver also has internal gate resistors for minimum external component count. The charge and trigger voltage logic thresholds are set at 1.3  $V_{HI}(min)$  to support applications implementing low-voltage control logic.

The A8740 is available in an 8-contact 2 mm  $\times$  2 mm DFN/MLP package with a 0.60 maximum overall package height, and an exposed pad for enhanced thermal performance. It is lead (Pb) free with 100% matter tin leadframe plating.

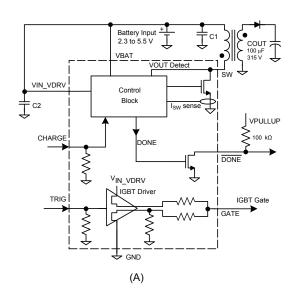

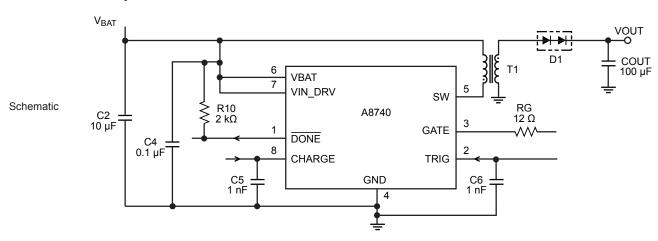

### **Typical Applications**

Figure 1. Typical applications: (A) with single battery supply and (B) with separate bias supply

**Selection Guide**

| Part Number  | Packing              | Package                                    |  |  |

|--------------|----------------------|--------------------------------------------|--|--|

| A8740EEETR-T | 3000 pieces per reel | 8-contact DFN/MLP with exposed thermal pad |  |  |

### **Absolute Maximum Ratings**

| Characteristic                | Characteristic Symbol Notes |                                                                                                                                                                                                                     | Rating                          | Units       |  |

|-------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------|--|

| SW Pin                        | V <sub>SW</sub>             | DC voltage. (V <sub>SW</sub> is self-clamped by internal active clamp and is allowed to exceed 50 V during flyback spike durations. Maximum repetitive energy during flyback spike: 0.5 µJ at frequency ≤ 400 kHz.) | -0.3 to 50                      | <b>&gt;</b> |  |

|                               | I <sub>SW</sub>             | DC current, pulse width = 1 ms                                                                                                                                                                                      | 3                               | Α           |  |

| VIN_DRV, VBAT Pins            | V <sub>IN</sub>             |                                                                                                                                                                                                                     | -0.3 to 6.0                     | V           |  |

| CHARGE, TRIG, DONE Pins       |                             | Care should be taken to limit the current when –0.6 V is applied to these pins.                                                                                                                                     | -0.6 to V <sub>IN</sub> + 0.3 V | V           |  |

| Remaining Pins                |                             |                                                                                                                                                                                                                     | -0.3 to V <sub>IN</sub> + 0.3 V | V           |  |

| Operating Ambient Temperature | T <sub>A</sub>              | Range E                                                                                                                                                                                                             | -40 to 85                       | °C          |  |

| Maximum Junction              | T <sub>J</sub> (max)        |                                                                                                                                                                                                                     | 150                             | °C          |  |

| Storage Temperature           | T <sub>stg</sub>            |                                                                                                                                                                                                                     | -55 to 150                      | °C          |  |

### THERMAL CHARACTERISTICS may require derating at maximum conditions

| Characteristic             | Symbol          | Test Conditions*                     | Value | Units |

|----------------------------|-----------------|--------------------------------------|-------|-------|

| Package Thermal Resistance | $R_{\theta JA}$ | 4-layer PCB, based on JEDEC standard | 49    | °C/W  |

<sup>\*</sup>Additional thermal information available on Allegro Web site.

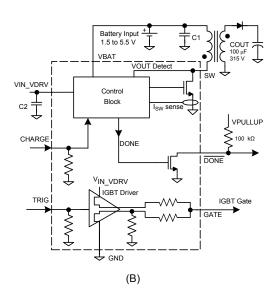

### **Functional Block Diagram**

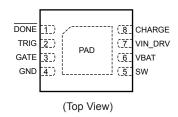

### **Pin-out Diagram**

#### **Terminal List**

| Number | Name    | Function                                                                                                                                              |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DONE    | Open collector output, pulls low when output reaches target value and CHARGE is high. Goes high during charging or whenever CHARGE is low.            |

| 2      | TRIG    | IGBT trigger input.                                                                                                                                   |

| 3      | GATE    | IGBT gate drive output.                                                                                                                               |

| 4      | GND     | Ground connection.                                                                                                                                    |

| 5      | SW      | Drain connection of internal DMOS switch. Connect to transformer primary winding.                                                                     |

| 6      | VBAT    | Battery voltage.                                                                                                                                      |

| 7      | VIN_DRV | Input voltage. Connect to 3 to 5.5 V bias supply. Decouple $V_{\text{IN}}$ voltage with 0.1 $\mu\text{F}$ ceramic capacitor placed close to this pin. |

| 8      | CHARGE  | Charge enable pin. Set this pin low to shut down the chip.                                                                                            |

| _      | PAD     | Exposed pad for enhanced thermal dissipation. Connect to ground plane.                                                                                |

### A8740

# Ultra Small Mobile Phone Xenon Photoflash Capacitor Charger with IGBT Driver

**ELECTRICAL CHARACTERISTICS** Typical values are valid at  $V_{IN} = V_{BAT} = 3.6 \text{ V}$ ;  $T_A = 25^{\circ}\text{C}$ , except • indicates specifications guaranteed from -40°C to 85°C ambient, unless otherwise noted

| Characteristics                             | Symbol                 | Test Conditions                                                               | Min.  | Тур. | Max. | Unit |

|---------------------------------------------|------------------------|-------------------------------------------------------------------------------|-------|------|------|------|

| VBAT Voltage Range <sup>1</sup>             | $V_{BAT}$              |                                                                               | • 1.5 | _    | 5.5  | V    |

| VIN_DRV Voltage Range <sup>1</sup>          | V <sub>IN</sub>        |                                                                               | • 2.3 | _    | 5.5  | V    |

| UVLO Enable Threshold                       | V <sub>INUV</sub>      | V <sub>IN</sub> rising                                                        | _     | 2.05 | 2.2  | V    |

| UVLO Hysteresis                             | V <sub>INUV(hys)</sub> |                                                                               | _     | 150  | _    | mV   |

|                                             | I <sub>IN</sub>        | Shutdown (CHARGE = 0 V, TRIG = 0 V)                                           | _     | 0.02 | 0.5  | μA   |

| V <sub>IN</sub> Supply Current              |                        | Charging complete                                                             | _     | 50   | 100  | μA   |

|                                             |                        | Charging (CHARGE = V <sub>IN</sub> , TRIG = 0 V)                              | _     | 2    | -    | mA   |

|                                             |                        | Shutdown (CHARGE = 0 V, TRIG = 0 V)                                           | _     | 0.01 | 1    | μA   |

| VBAT Pin Supply Current                     | I <sub>BAT</sub>       | Charging done (CHARGE = V <sub>IN</sub> ,<br>DONE = 0 V)                      | -     | _    | 5    | μA   |

|                                             |                        | Charging (CHARGE = V <sub>IN</sub> , TRIG = 0 V)                              | _     | _    | 50   | μA   |

| Current Limit                               |                        |                                                                               | ·     |      |      |      |

| Primary-Side Current Limit <sup>2</sup>     | I <sub>SWLIM</sub>     |                                                                               | 1.35  | 1.5  | 1.65 | Α    |

| Switch On-Resistance                        | R <sub>SWDS(on)</sub>  | $V_{IN\_DRV} = 3.6 \text{ V}, I_D = 600 \text{ mA}, T_A = 25^{\circ}\text{C}$ | _     | 0.4  | _    | Ω    |

| Switch Leakage Current <sup>1</sup>         | I <sub>SWLK</sub>      | V <sub>SW</sub> = 5.5, over full temperature range                            | • -   | _    | 2    | μA   |

| CHARGE Pull-down Resistance                 | R <sub>CHGPD</sub>     |                                                                               | _     | 130  | _    | kΩ   |

| 01117071 11111 1                            |                        | High, over input supply range                                                 | • 1.3 | _    | _    | V    |

| CHARGE Input Voltage <sup>1</sup>           | V <sub>CHARGE</sub>    | Low, over input supply range                                                  | • -   | _    | 0.5  | V    |

| CHARGE On/Off Delay                         | t <sub>CH</sub>        | Time between CHARGE = 1 and charging enabled                                  | -     | 20   | _    | us   |

| Switch-Off Timeout                          | t <sub>off(max)</sub>  |                                                                               | _     | 18   | _    | μs   |

| Switch-On Timeout                           | t <sub>on(max)</sub>   |                                                                               | _     | 18   | _    | μs   |

| Output Comparator Trip Voltage <sup>3</sup> | V <sub>OUTTRIP</sub>   | Measured as V <sub>SW</sub> – V <sub>BAT</sub>                                | 31.0  | 31.5 | 32.0 | V    |

| Output Comparator Voltage Overdrive         | V <sub>OUTOV</sub>     | Pulse width = 200 ns (90% to 90%)                                             | _     | 200  | 400  | mV   |

| DONE Output Leakage Current <sup>1</sup>    | I <sub>DONELK</sub>    |                                                                               | • -   | _    | 1    | μA   |

| DONE Output Low Voltage <sup>1</sup>        | V <sub>DONEL</sub>     | 32 μA into DONE pin                                                           | • -   | _    | 100  | mV   |

| dV/dt Threshold for ZVS Comparator          | dV/dt                  | Measured at SW pin                                                            | _     | 20   | _    | V/µs |

| IGBT Driver                                 |                        |                                                                               | '     | '    |      |      |

| TRICL WITH 1                                | V <sub>TRIG(H)</sub>   | Input = logic high, over input supply range                                   | • 1.3 | _    | _    | V    |

| TRIG Input Voltage <sup>1</sup>             | V <sub>TRIG(L)</sub>   | Input = logic low, over input supply range                                    | • -   | _    | 0.5  | V    |

| TRIG Pull-Down Resistor                     | R <sub>TRIGPD</sub>    |                                                                               | _     | 130  | _    | kΩ   |

| GATE Resistance to VIN_DRV                  | R <sub>SrcDS(on)</sub> | V <sub>GATE</sub> = 1.8 V                                                     | _     | 6.6  | _    | Ω    |

| GATE Resistance to GND                      | R <sub>SnkDS(on)</sub> | V <sub>GATE</sub> = 1.8 V                                                     | _     | 50   | _    | Ω    |

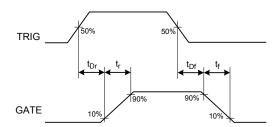

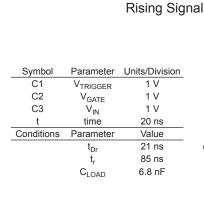

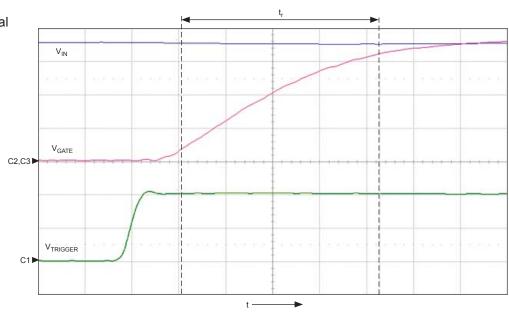

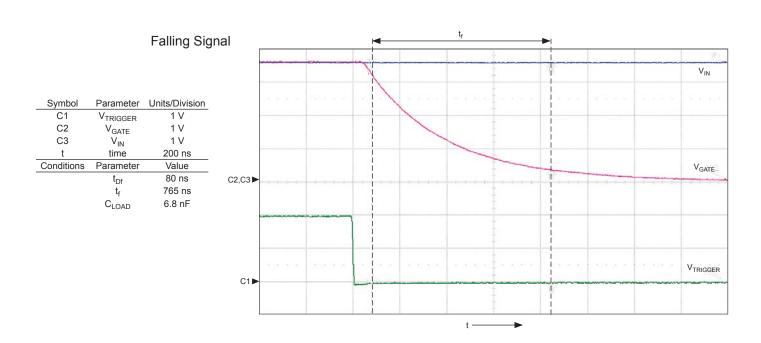

| Propagation Delay (Rising) <sup>4,5</sup>   | t <sub>Dr</sub>        | Measurement taken at DONE pin, C <sub>L</sub> = 6500 pF                       | _     | 25   | -    | ns   |

| Propagation Delay (Falling) <sup>4,5</sup>  | t <sub>Df</sub>        |                                                                               | _     | 60   | _    | ns   |

| Output Rise Time <sup>4,5</sup>             | t <sub>r</sub>         |                                                                               | _     | 80   | _    | ns   |

| Output Fall Time <sup>4,5</sup>             | t <sub>f</sub>         |                                                                               | -     | 700  | -    | ns   |

| GATE Pull-Down Resistor                     | R <sub>GTPD</sub>      |                                                                               | _     | 20   | -    | kΩ   |

$<sup>^{1}</sup>$ Specifications throughout the range  $T_A$  =  $-40^{\circ}$ C to  $85^{\circ}$ C guaranteed by design and characterization.

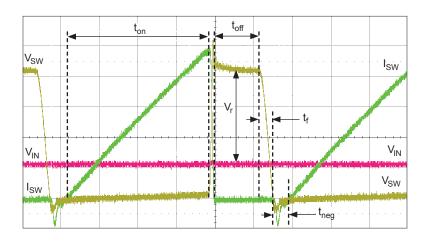

<sup>&</sup>lt;sup>5</sup>See IGBT Drive Timing Definition diagram for further information.

<sup>&</sup>lt;sup>2</sup>Current limit guaranteed by design and correlation to static test.

$<sup>^3</sup>$ Specifications throughout the range  $T_A$  =  $-20^{\circ}$ C to  $85^{\circ}$ C guaranteed by design and characterization.

<sup>&</sup>lt;sup>4</sup>Guaranteed by design and characterization.

### **IGBT Drive Timing Definition**

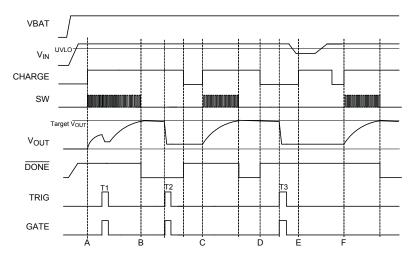

### **Operation Timing Diagram**

#### **Explanation of Events**

- A: Start charging by pulling CHARGE to high, provided that  $V_{\mbox{\footnotesize{IN}}}$  is above UVLO level.

- B: Charging stops when  $V_{\mbox{\scriptsize OUT}}$  reaches the target voltage

- C: Start a new charging process with a low-to-high transition at the CHARGE pin.

- D: Pull CHARGE to low to put the controller in low-power standby mode.

- E: Charging does not start, because  $V_{\mbox{\footnotesize{IN}}}$  is below UVLO level when CHARGE goes high.

- F: After  $V_{\mbox{\scriptsize IN}}$  goes above UVLO, another low-to-high transition at the CHARGE pin is required to start the charging.

- T1, T2, T3 (Trigger instances): IGBT driver output pulled high whenever the TRIG pin is at logic high. It is recommended to avoid applying any trigger pulses during charging.

### **Characteristic Performance**

#### **IGBT Drive Performance**

IGBT drive waveforms are measured at pin, with capacitive load of 6800 pF

6

### **Characteristic Performance**

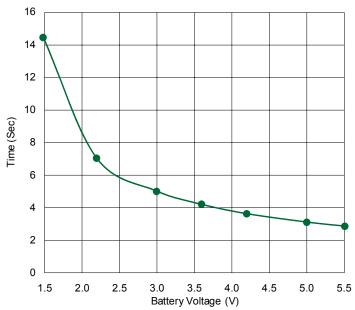

### **Efficiency versus Battery Voltage**

Transformer  $L_{PRIMARY}$  = 12.8  $\mu$ H, N =10.25,  $V_{IN}$  =3.6 V, at room temperature

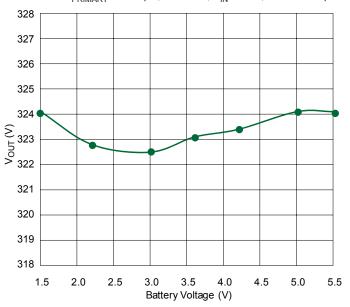

Final Output Voltage versus Battery Voltage

Transformer  $L_{PRIMARY}$  = 12.8  $\mu$ H, N =10.25,  $V_{IN}$  =3.6 V, at room temperature

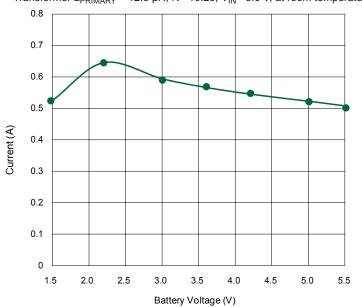

### **Average Input Current versus Battery Voltage**

Transformer  $L_{PRIMARY}$  = 12.8  $\mu$ H, N =10.25,  $V_{IN}$  =3.6 V, at room temperature

Note: Peak switch current is limited by the maximum on-time and di/dt of the transformer primary current; therefore, average input current drops at very low battery voltage.

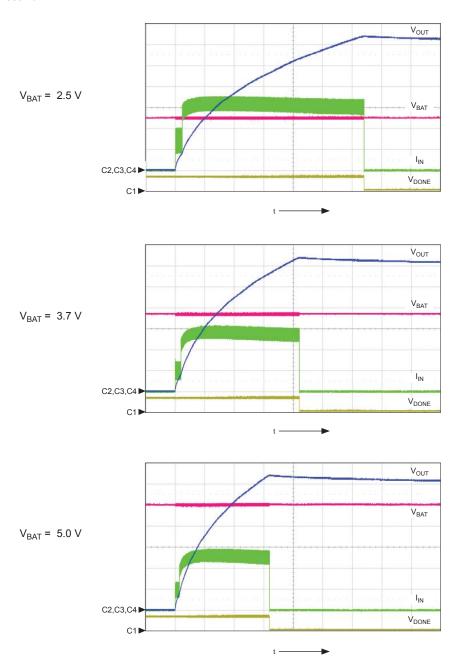

### **Charging Waveforms**

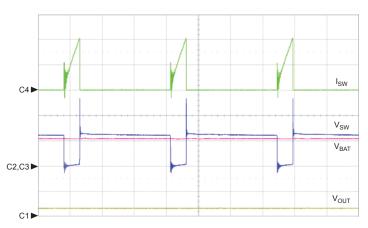

### **Output Capacitor Charging at Various Battery Voltages**

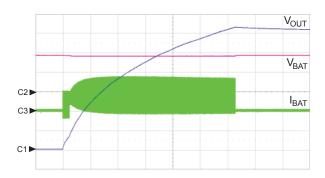

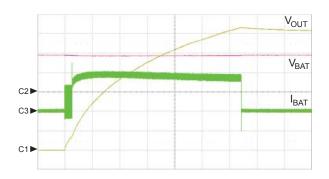

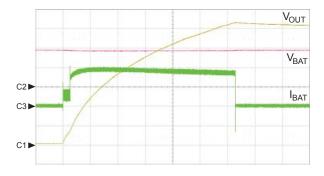

Test conditions:  $V_{IN}$  = 3.6 V,  $C_{OUT}$  = 100  $\mu$ F / 330 V UCC, transformer = T-16-024A ( $L_{PRIMARY}$  =12.8  $\mu$ H, N = 10.25), at room temperature Oscilloscope settings: Ch1 = DONE (5 V / div), Ch2 = Battery Voltage (1 V / div), Ch3 = Output Voltage (50 V / div), Ch4 = Input Current (200 mA V / div), Time scale = 1 sec / div

### **Functional Description**

#### **General Operation Overview**

The charging operation is started by a low-to-high signal on the CHARGE pin, provided that  $V_{\rm IN}$  is above the  $V_{\rm UVLO}$  level. It is strongly recommended to keep the CHARGE pin at logic low during power-up. After  $V_{\rm IN}$  exceeds the UVLO level, a low-to-high transition on the CHARGE pin is required to start the charging. The  $\overline{\rm DONE}$  open-drain indicator is pulled low when CHARGE is high and target output voltage is reached.

When a charging cycle is initiated, the transformer primary side current,  $I_{PRIMARY}$ , ramps-up linearly at a rate determined by the combined effect of the battery voltage,  $V_{BAT}$ , and the primary side inductance,  $L_{PRIMARY}$ . When  $I_{PRIMARY}$  reaches the current limit,  $I_{SWLIM}$ , the internal MOSFET is turned off immediately, allowing the energy to be pushed into the photoflash capacitor,  $C_{OUT}$ , from the secondary winding. The secondary side current drops linearly as  $C_{OUT}$  charges. The switching cycle starts again, either after the transformer flux is reset, or after a predetermined time period,  $t_{OFF}(max)$  (18 µs), whichever occurs first.

The A8740 senses output voltage indirectly on primary side. This eliminates the need for high voltage feedback resistors required for secondary sensing. Flyback converter stops switching when output voltage reaches:

$$V_{\text{OUT}} = K \times N - V_{\text{d}}$$

,

Where:

K = 31.5 V typically,

$V_d$  is the forward drop of the output diode (approximately 2 V), and

N is transformer turns ratio.

#### Switch On-Time and Off-Time Control

The A8740 implements an adaptive on-time/off-time control. Ontime duration, t<sub>on</sub>, is approximately equal to

$$t_{\rm on} = I_{\rm SWlim} \times L_{\rm PRIMARY} / V_{\rm BAT}$$

.

Off-time duration, t<sub>off</sub>, depends on the operating conditions during switch off-time. The A8740 applies two charging modes: Fast Charging mode and Timer mode, according to the conditions described in the next section.

#### **Timer Mode and Fast Charging Mode**

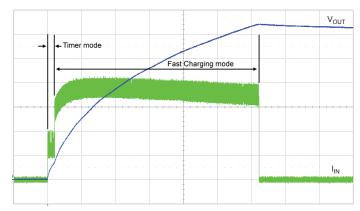

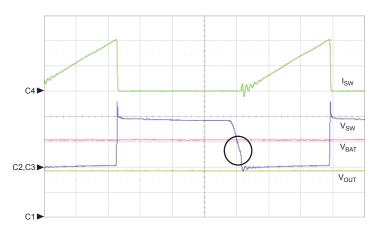

The A8740 achieves fast charging times and high efficiency by operating in discontinuous conduction mode (DCM) through most of the charging process. The relationship of Timer mode and Fast Charging mode is shown in figure 2.

The IC operates in Timer mode when beginning to charge a completely discharged photoflash capacitor, usually when the output voltage,  $V_{OUT}$ , is less than approximately 30 V (depending on transformer used). Timer mode is a fixed period, 18  $\mu$ s, off-time control. One advantage of having Timer mode is that it limits the initial battery current surge and thus acts as a "soft-start." A time-expanded view of a Timer mode interval is shown in figure 3.

Figure 2. Timer mode and Fast Charging mode: t = 1 s/div;  $V_{OUT}$  = 50 V/div;  $I_{IN}$  = 150 mA/div.,  $V_{IN}$  =  $V_{BAT}$  = 3.6 V;  $C_{OUT}$  = 100  $\mu$ F/330 V; and ILIM = 1.0 A.

Figure 3. Expanded view of Timer mode:  $V_{OUT} \le 10 \text{ V}$ ,  $V_{BAT} = 5.5 \text{ V}$ , Ch1:  $V_{OUT} = 20 \text{ V/div.}$ , Ch2:  $V_{BAT} = 5 \text{ V/div.}$ , Ch3:  $V_{SW} = 5 \text{ V/div.}$ , Ch4:  $I_{SW} = 750 \text{ mA/div.}$ , t = 5 µs/div.

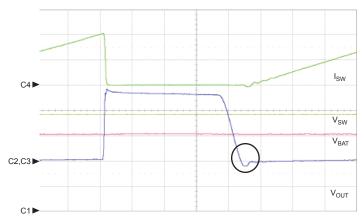

As soon as a sufficient voltage has built up at the output capacitor, the IC enters Fast-Charging mode. In this mode, the next switching cycle starts after the secondary side current has stopped flowing, and the switch voltage has dropped to a minimum value. A proprietary circuit is used to allow minimum-voltage switching, even if the SW pin voltage does not drop to 0 V. This enables

Fast-Charging mode to start earlier, thereby reducing the overall charging time. Minimum-voltage switching is shown in figure 4.

During Fast-Charging mode, when  $V_{OUT}$  is high enough (over 50 V), true zero-voltage switching (ZVS) is achieved. This further improves efficiency as well as reduces switching noise. A ZVS interval is shown in figure 5.

Figure 4. Minimum-voltage switching:  $V_{OUT} \ge 35 \text{ V}$ ,  $V_{BAT} = 5.5 \text{ V}$ , Ch1:  $V_{OUT} = 20 \text{ V/div.}$ , Ch2:  $V_{BAT} = 5 \text{ V/div.}$ , Ch3:  $V_{SW} = 5 \text{ V/div.}$ , Ch4:  $I_{SW} = 750 \text{ mA/div.}$ , t = 1 µs/div.

Figure 5. True zero-voltage switching (ZVS):  $V_{OUT}$  = 75 V,  $V_{BAT}$  = 5.5 V, Ch1:  $V_{OUT}$  = 20 V/div., Ch2:  $V_{BAT}$  = 5 V/div., Ch3:  $V_{SW}$  = 5 V/div., Ch4:  $I_{SW}$  = 750 mA/div., t = 0.5  $\mu$ s / div.

### **Applications Information**

#### **Transformer Design**

1. The transformer turns ratio, N, determines the output voltage:

$$N = N_{\rm S} / N_{\rm P}$$

$$V_{\rm OUT} = 31.5 \times N - V_{\rm d} ,$$

where 31.5 is the typical value of  $V_{OUTTRIP}$ , and  $V_d$  is the forward drop of the output diode.

2. The primary inductance,  $L_{\mbox{\scriptsize PRIMARY}}$ , determines the on-time of the switch:

$$t_{\rm on} = (-L_{\rm PRIMARY}/R) \times \ln(1 - I_{\rm SWlim} \times R/V_{\rm IN})$$

,

where R is the total resistance in the primary current path (including  $R_{SWDS(on)}$  and the DC resistance of the transformer).

If  $V_{IN}$  is much larger than  $I_{SWlim} \times R,$  then  $t_{on}$  can be approximated by:

$$t_{\rm on} = I_{\rm SWlim} \times L_{\rm PRIMARY} / V_{\rm IN}$$

.

3. The secondary inductance, L<sub>SECONDARY</sub>, determines the off-time of the switch. Given:

$$\begin{split} L_{\text{SECONDARY}} / L_{\text{PRIMARY}} &= N \times N \text{, then} \\ t_{\text{off}} &= (I_{\text{SWlim}} / N) \times L_{\text{SECONDARY}} / V_{\text{OUT}} \\ &= (I_{\text{SWlim}} \times L_{\text{PRIMARY}} \times N) / V_{\text{OUT}} \end{split} .$$

The minimum pulse width for  $t_{off}$  determines what is the minimum  $L_{PRIMARY}$  required for the transformer. For example, if ILIM = 1.5 A, N = 10, and  $V_{OUT}$  = 315 V, then  $L_{PRIMARY}$  must be at least 4.2  $\mu$ H in order to keep  $t_{off}$  at 200 ns or longer. These relationships are illustrated in figure 6.

In general, choosing a transformer with a larger  $L_{PRIMARY}$  results in higher efficiency (because a larger  $L_{PRIMARY}$  corresponds to a lower switch frequency and hence lower switching loss). But transformers with a larger  $L_{PRIMARY}$  also require more windings and larger magnetic cores. Therefore, a trade-off must be made between transformer size and efficiency.

#### Leakage Inductance and Secondary Capacitance

The transformer design should minimize the leakage inductance to ensure the turn-off voltage spike at the SW node does not exceed the absolute maximum specification on the SW pin (refer to the Absolute Maximum Ratings table). An achievable minimum leakage inductance for this application, however, is usually compromised by an increase in parasitic capacitance. Furthermore, the transformer secondary capacitance should be minimized. Any secondary capacitance is multiplied by N² when reflected to the primary, leading to high initial current swings when the switch turns on, and to reduced efficiency.

Figure 6. Transformer Selection Relationships

#### **Input Capacitor Selection**

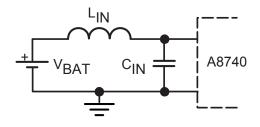

Ceramic capacitors with X5R or X7R dielectrics are recommended for the input capacitor,  $C_{\rm IN}$ . During initial Timer mode the device operates with 18  $\mu s$  off-time. The resonant period caused by input filter inductor and capacitor should be at least 2 times greater or smaller than the 18  $\mu s$  Timer period, to reduce input ripple current during this period. The typical input LC filter is shown in figure 7.

The resonant period is given by:

$$T_{\rm res} = 2 \pi (L \times C_{\rm IN})^{1/2}$$

.

The effects of input filter components are shown in figures 8, 9, and 10. It is recommended to use at least 10  $\mu F$  / 6.3 V to decouple the battery input, VBAT , at the primary of the transformer. Decouple the VIN pin using 0.1  $\mu F$  / 6.3 V bypass capacitor.

#### **Output Diode Selection**

Choose rectifying diodes, D1, to have small parasitic capacitance (short reverse recovery time) while satisfying the reverse voltage and forward current requirements. The peak reverse voltage of the diodes,  $V_{DPeak}$ , occurs when the internal MOSFET switch is closed. It can be calculated as:

$$V_{\mathrm{DPeak}} = V_{\mathrm{OUT}} + N \times V_{\mathrm{BAT}}$$

.

The peak current of the rectifying diode,  $I_{DPeak}$ , is calculated as:

$$I_{\text{DPeak}} = I_{\text{PRIMARY Peak}} / N$$

.

Figure 7. Typical input section with input inductance (inductance,  $L_{\text{IN}}$ , may be an input filter inductor or inductance due to long wires in test setup)

#### Effects of Input Filters

Figure 8. Input current waveforms with Li+ battery connected by 5-in. wire and decoupled by 4.7  $\mu$ F capacitor,  $C_{OUT}$  = 100  $\mu$ F,  $V_{IN} = V_{BAT} = 3.6$  V, Ch1:  $V_{OUT} = 50$  V/div, Ch2:  $V_{BAT} = 2$  V/div, Ch3:  $I_{BAT} = 750$  mA/div, t = 1 s/div

Figure 9. Input current waveforms with Li+ battery connected through 4.7  $\mu$ H inductor and 4.7  $\mu$ F capacitor, C<sub>OUT</sub> = 100  $\mu$ F, V<sub>IN</sub> = V<sub>BAT</sub> = 3.6 V, Ch1: V<sub>OUT</sub> = 50 V/div, Ch2: V<sub>BAT</sub> = 2 V/div, Ch3: I<sub>BAT</sub> = 300 mA/div, t = 1 s/div

Figure 10. Input current waveforms with Li+ battery connected through 4.7  $\mu$ H inductor and 10  $\mu$ F capacitor, C<sub>OUT</sub> = 100  $\mu$ F, V<sub>IN</sub> = V<sub>BAT</sub> = 3.6 V, Ch1: V<sub>OUT</sub> = 50 V/div, Ch2: V<sub>BAT</sub> = 2 V/div, Ch3: I<sub>BAT</sub> = 300 mA/div, t = 1 s/div

### A8740

## Ultra Small Mobile Phone Xenon Photoflash Capacitor Charger with IGBT Driver

#### **Layout Guidelines**

Key to a good layout for the photoflash capacitor charger circuit is to keep the parasitics minimized on the power switch loop (transformer primary side) and the rectifier loop (secondary side). Use short, thick traces for connections to the transformer primary and SW pin. It is important that the  $\overline{\rm DONE}$  signal trace and other signal traces be routed away from the transformer and other switching traces, in order to minimize noise pickup. In addition, high voltage isolation rules must be followed carefully to avoid

breakdown failure of the circuit board.

Avoid placing any ground plane area underneath the transformer secondary and diode, to minimize parasitic capacitance.

Connect the EE package PAD to the ground pad for better thermal performance. Use ground planes on the top and bottom layers below the IC and connect them through multiple thermal vias. Refer to the figures on page 18 for recommended layout.

#### **Recommended Components**

| Component                     | Rating                                                        | Part Number       | Source                                            |

|-------------------------------|---------------------------------------------------------------|-------------------|---------------------------------------------------|

| C1, Input Capacitor           | 10 μF, ±10%, 6.3 V, X5R ceramic capacitor (0805)              | JMK212BJ106K      | Taiyo Yuden                                       |

| C2                            | 0.1 μF, 6.3 V X5R ceramic capacitor                           |                   |                                                   |

| COUT, Photoflash<br>Capacitor | 100 μF / 330 V                                                | EPH-31ELL101B131S | Chemi-Con                                         |

| D1, Output Diode              | 2 x 250 V, 225 mA, 5 pF                                       | BAV23S            | Philips Semiconductor,<br>Fairchild Semiconductor |

| T1, Transformer               | L <sub>PRIMARY</sub> = 12.8 μH, N= 10.25,<br>6.5 × 8 × 4 mm   | T-16-024A         | Tokyo Coil Electric                               |

|                               | $L_{PRIMARY} = 6 \mu H, N = 10.4, 5.6 \times 5.6 \times 3 mm$ | LDT565630T-001    | TDK                                               |

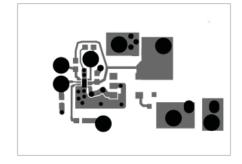

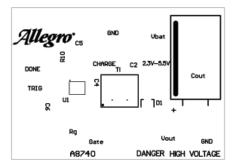

#### **Recommended Layout**

Top side

Bottom side

Top components

### Package EE 8-Contact DFN with Exposed Thermal Pad

A8740

### Ultra Small Mobile Phone Xenon Photoflash Capacitor Charger with IGBT Driver

Copyright ©2011, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com

17